#### Andor Menczer

#### MASSIVELY PARALLEL TENSOR NETWORK ALGORITHMS

Supervisors: Dr. Tamás Kozsik (ELTE), Dr. Örs Legeza (Wigner) Note: these slides only function as an outline, therefore they are not to be used without giving further explanation

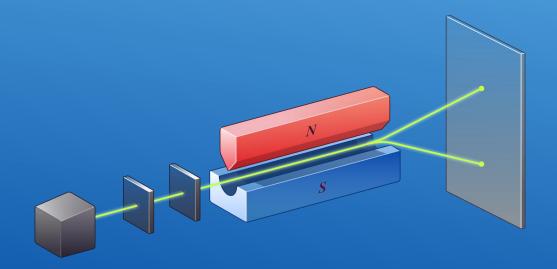

## **ELECTRON SPIN**

Spinning electrons? Whaaat? How do they do that?

#### ELECTRONS ARE SPINNING BALLS

... except they are not spinning

... and they aren't balls either

#### ENTANGLEMENT OF ELECTRONS

Subsystems cannot be described independently

Superposition and mixed states are common

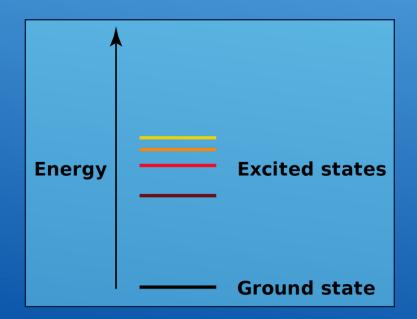

#### HAMILTONIAN

Description of the total energy level of the system

Ground state is defined as the eigen vector corresponding to the smallest possible eigenvalue

#### EXCITED QUANTUM SYSTEMS

Entanglement → combinatorial explosion

Exact value of ground state cannot be calculated

Whole matrix representation  $\rightarrow$  Tensor network states

Operations on the network can be executed locally, thus a polynomial solution becomes available

## **GPU ACCELERATION**

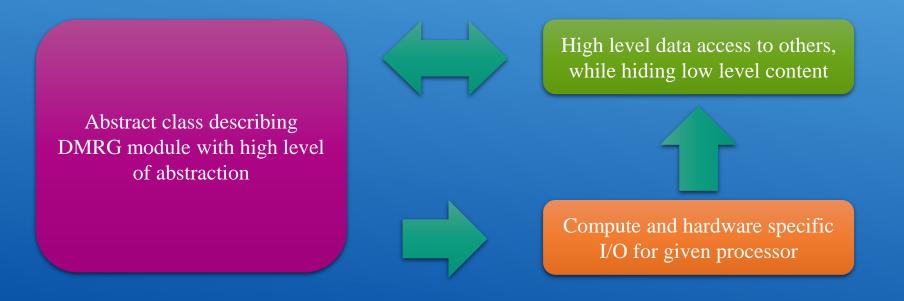

Restructuring monolithic CPU code for modular CPU / GPU execution

#### MODULAR DESIGN

Base algorithm is decoupled from the way data is stored, processed and operated on

Data storage, access and their operations are universally designed without any specific algorithm attached to them

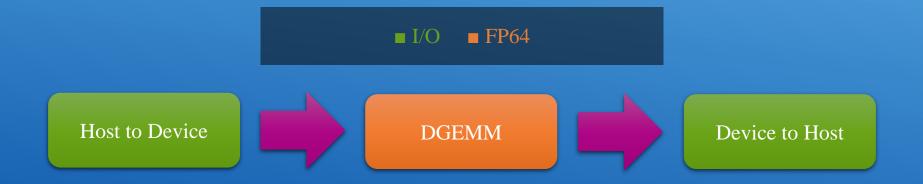

#### LARGER MATRICES

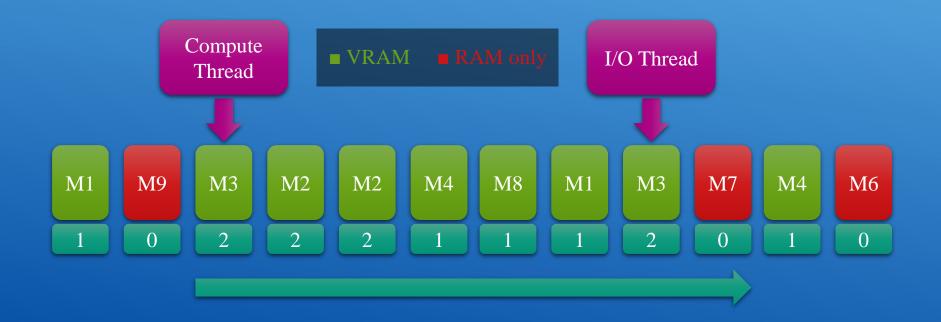

On the fly synchronous I/O  $\rightarrow$  Minimal VRAM requirement

O(n<sup>2</sup>) I/O time is masked by O(n<sup>3</sup>) FP64 time

#### I/O OF SMALLER MATRICES

Continuous asynchronous preloading on separate thread

I/O time is masked by running I/O and FP64 in parallel

#### COMPUTE OF SMALLER MATRICES

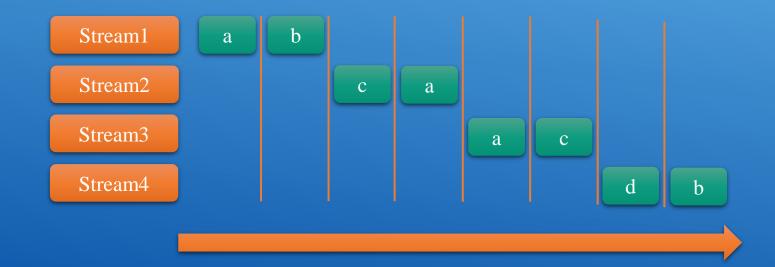

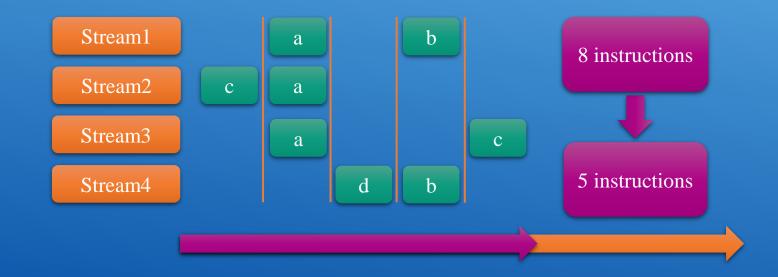

Batched DGEMM for deeply stacked matrices

Interleaved streams for heterogenous matrix sizes

#### INTERLEAVED STREAMS

Instruction sequence for each stream remains unchanged

Stacking the same instructions in each column  $\rightarrow$  SIMD

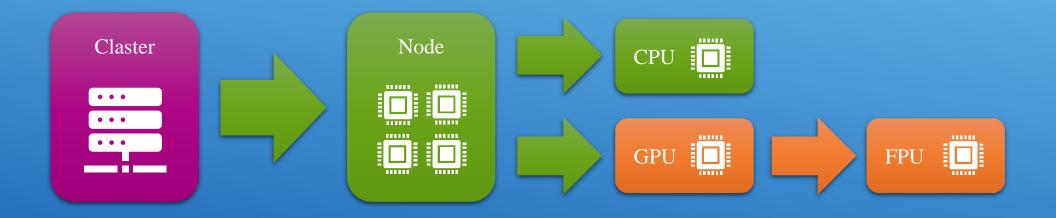

# HIGH LEVEL PARALLELIZATION

Optimizing TNS algorithms for HPC

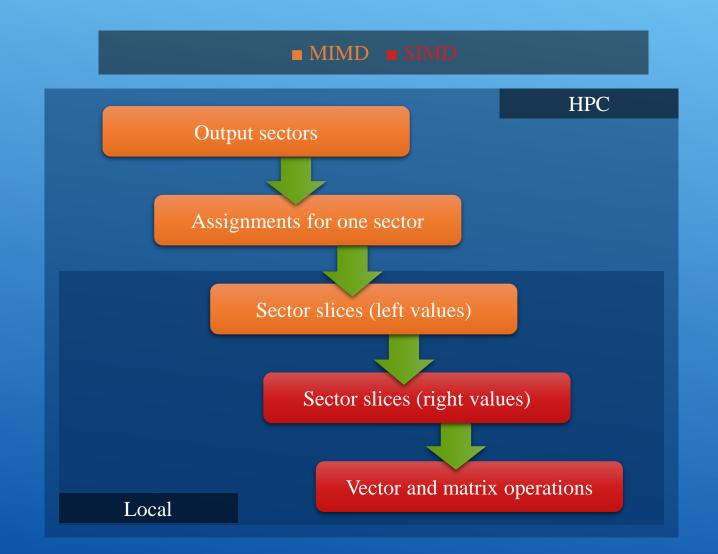

### MULTI-STAGE PARALLELIZATION

■ Producer ■ Task parallelism ■ Data parallelism

### SOFTWARE LAYERS

#### THANK YOU FOR YOUR ATTENTION!